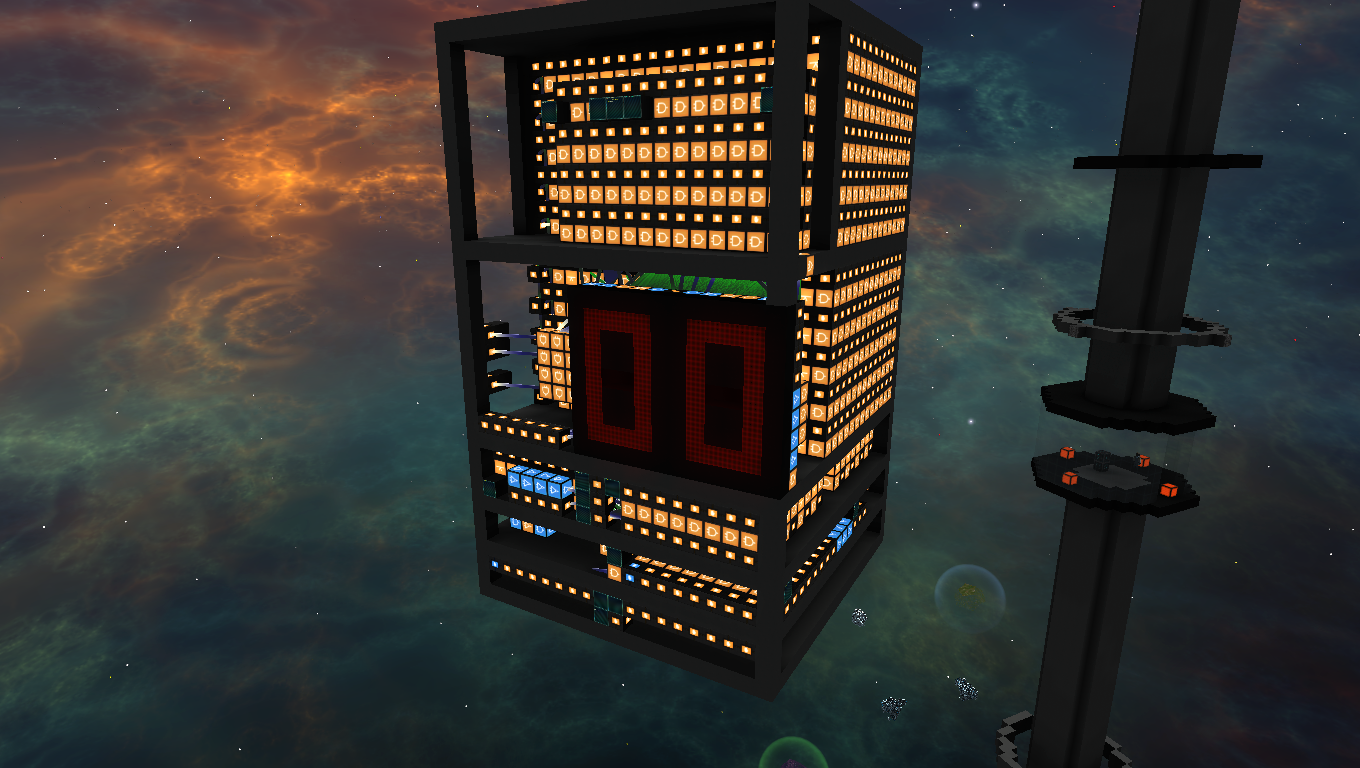

Logic Cortex model A: Logic Cortex

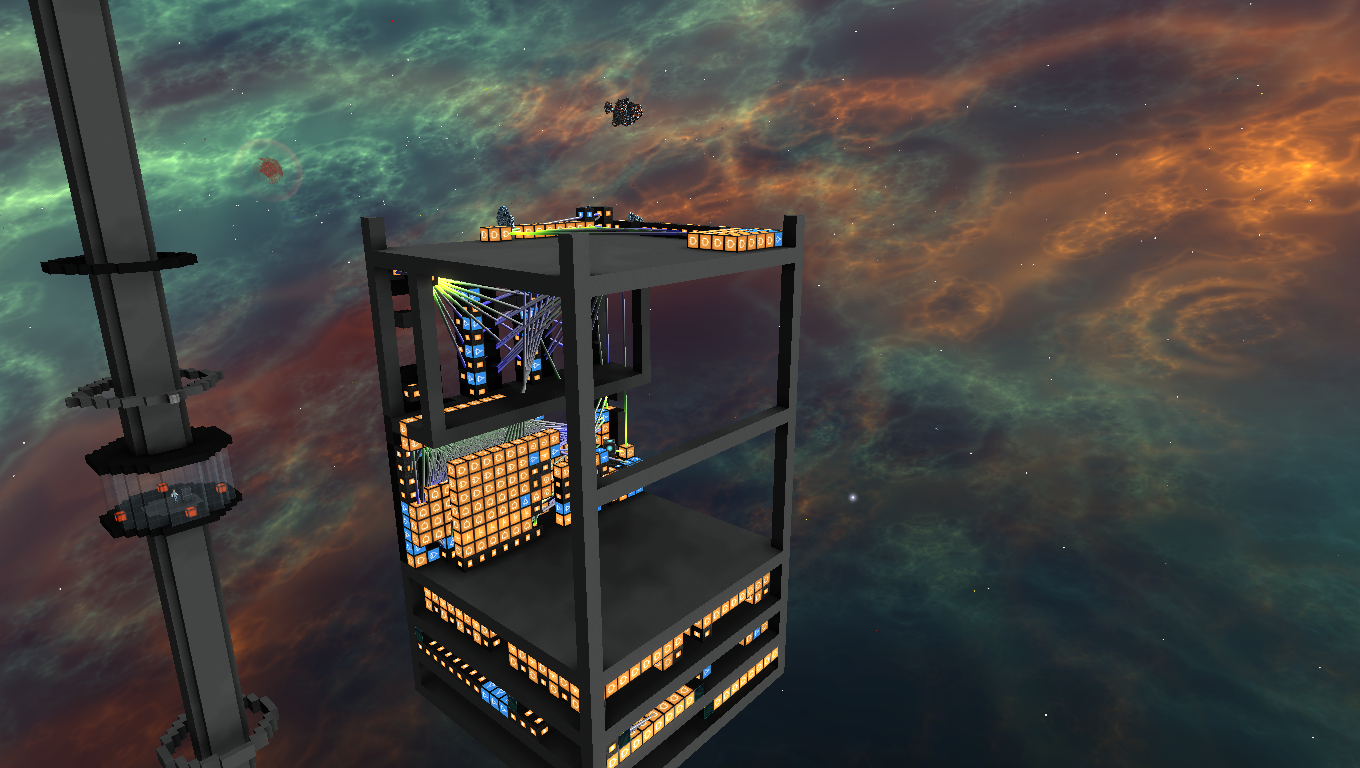

My first functioning computer in starmade.

My first functioning computer in starmade.

Since the fleet competition finished, I quickly realized that I no longer needed to crank out ships, so I instead decided to return to the logic side of things. Suffice it to say, I have got a bit carried away with this one:

This is the Logic Cortex Model A. My first foray into making a fully programmable microprocessor. It's intended use? To be put in anything that requires advanced control, like a giant robot. The intended specifications are as follows:

The intended specifications are as follows:

*4hz clock, hopefully allowing the system to execute one instruction cycle a second.

*32 I/O pins. With up to four configurable interrupts.

*16 8-bit registers.

*64 13-bit program memory cells. 4-bit oppcode, 1-bit to define whether the value is a constant, and an 8-bit value.

*Programming UI

*CU with at least 3kb of cache memory.

*ALU with add/subtract

*Shift Register

*Programmable Program Counter

*Support for the following instructions:

0000 Goto-Value(Resets program counter with a new value)

0001 StoreCache-C/R-Value(Stores a number in the cache. Storing 00000000 will clear the cache)

0010 Pinout-C/R-value(Outputs a value to the pins)

0011 PinsIn-Selection(in byte-long steps)

0100 Add-C/R-Value(added to cache, output by result)

0101 Subtract-C/R-Value(added to cache, output by result)

0110 Result-Memory Selection (Outputs the results of a calculation to a register)

0111 AND-C/R-Value(added to cache, output by result)

1000 OR-C/R-Value(added to cache, output by result)

1001 NAND-C/R-Value(added to cache, output by result)

1010 NOR-C/R-Value(added to cache, output by result)(with nothing in the cache, behaves like a NOT operation)

1011 XOR-C/R-Value(added to cache, output by result)

1100 A==B-Value(compared to cache, skips the next operation if false)

1101 A>B-Value(compared to cache, skips the next operation if false)

1110 A<B-Value(compared to cache, skips the next operation if false)

1111 <<-Left/Right(output by result)

If the programming is too difficult, I may alter the logic processor to take up less of the instruction set, or add another bit to each program cell to double my oppcodes.

A more speciffic account on how the processor will work: The entire processor hopefully will be clocked at 4hs, however, it will take all four quarters of a second to execute one instruction cycle. The first stage is reading the program memory, the second is translating it into an action and executing it, the third step is reading the resulting value, and the fourth is iterating the counter or executing a GOTO. The processor works on 3kb of cache memory. One is temporary storage for storing the B-variable, typically being loaded up with direct input from a constant or a register. The other is long term storage for the A-variable, which is accessed by the StoreCache instruction. The result is that it works with a smaller program memory cell, but it is relatively inefficient.

One thing I might try to do is change the program counter so that it can work with a pipeline. Difficulty is that it would have to pause on a GOTO every time in case the program can skip it. Any tips on how to reduce the time footprint, or increase the speed is appreciated.

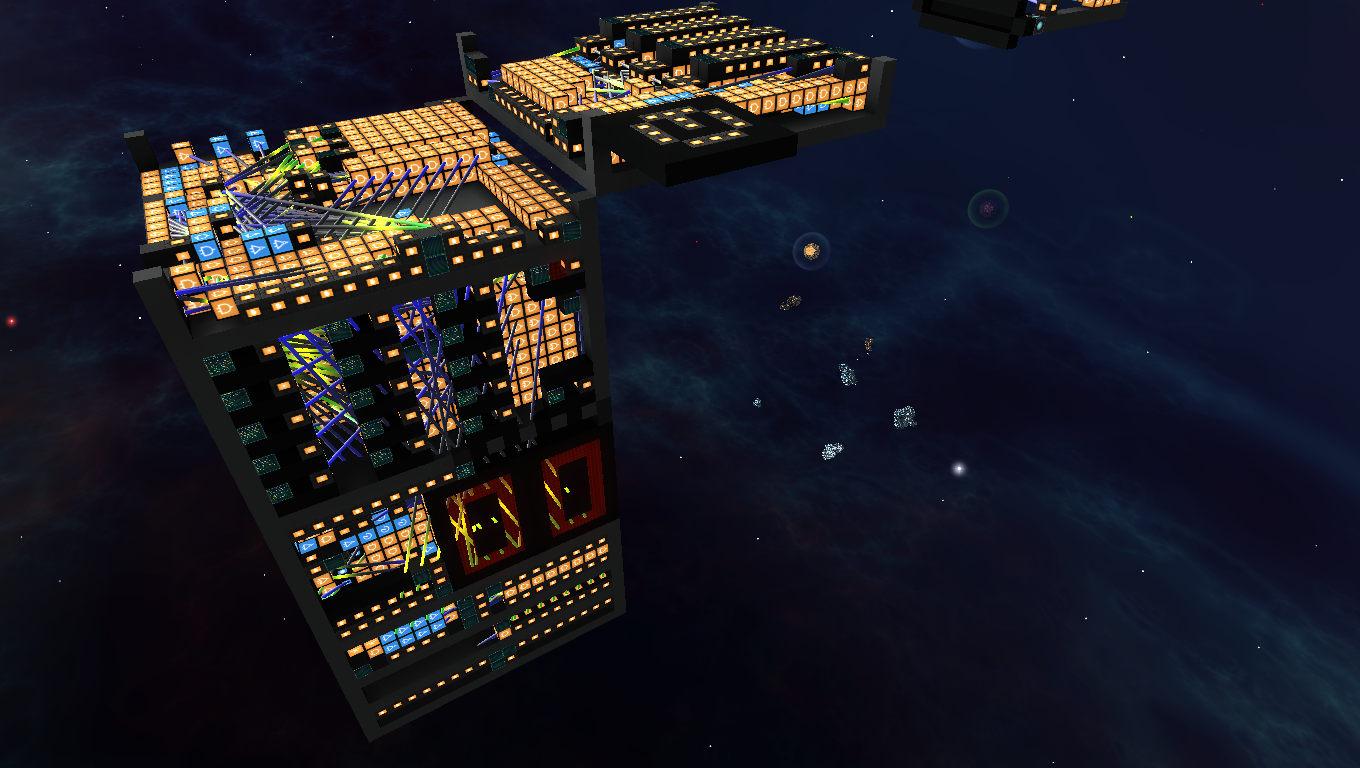

The only things I have not put in are the programming user interface, and the control unit. And possibly a pipeline if the system is too slow.

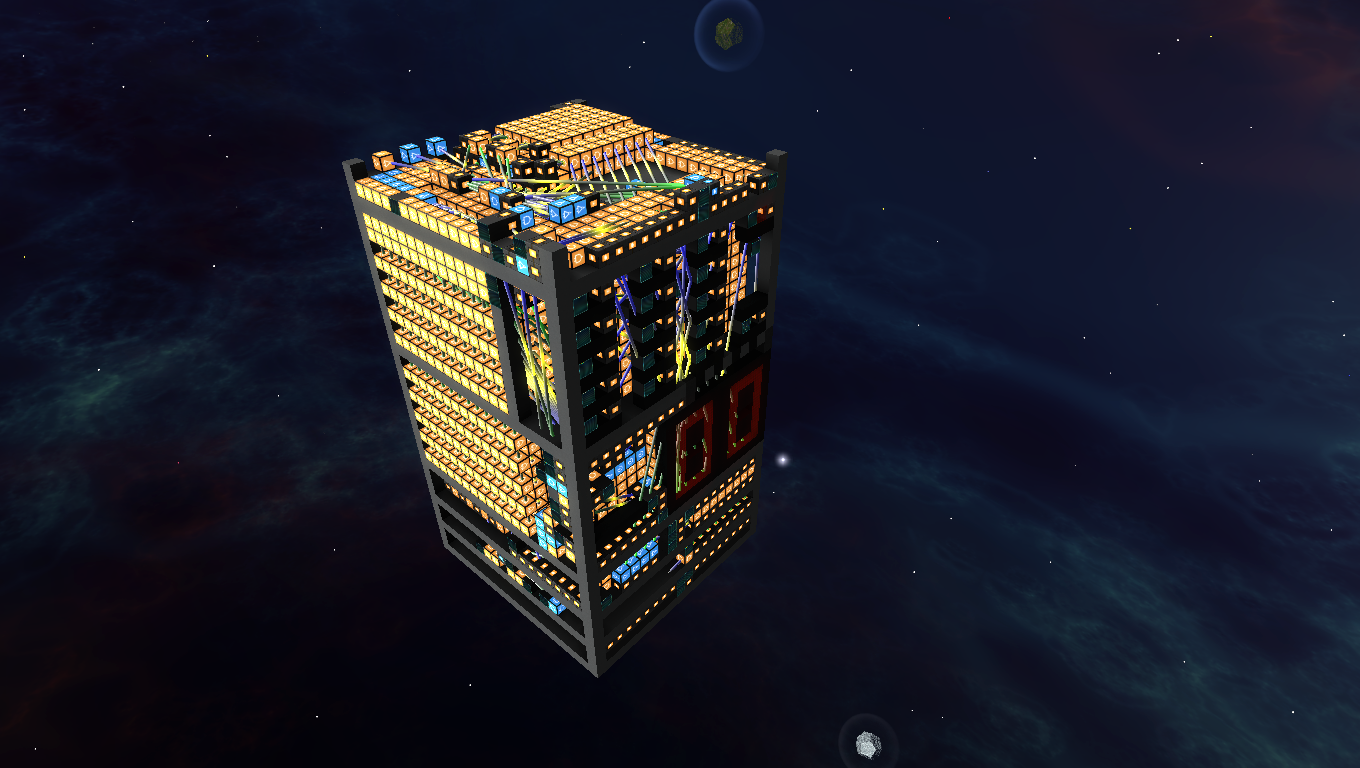

Another pic:

It is likely that I will perfect this over multiple iterations, as well as develop new models. I will document my progress on this thread.

Any tips and comments would be appreciated.

EDIT: Post reconstruction imminent!

This is the Logic Cortex Model A. My first foray into making a fully programmable microprocessor. It's intended use? To be put in anything that requires advanced control, like a giant robot.

*4hz clock, hopefully allowing the system to execute one instruction cycle a second.

*32 I/O pins. With up to four configurable interrupts.

*16 8-bit registers.

*64 13-bit program memory cells. 4-bit oppcode, 1-bit to define whether the value is a constant, and an 8-bit value.

*Programming UI

*CU with at least 3kb of cache memory.

*ALU with add/subtract

*Shift Register

*Programmable Program Counter

*Support for the following instructions:

0000 Goto-Value(Resets program counter with a new value)

0001 StoreCache-C/R-Value(Stores a number in the cache. Storing 00000000 will clear the cache)

0010 Pinout-C/R-value(Outputs a value to the pins)

0011 PinsIn-Selection(in byte-long steps)

0100 Add-C/R-Value(added to cache, output by result)

0101 Subtract-C/R-Value(added to cache, output by result)

0110 Result-Memory Selection (Outputs the results of a calculation to a register)

0111 AND-C/R-Value(added to cache, output by result)

1000 OR-C/R-Value(added to cache, output by result)

1001 NAND-C/R-Value(added to cache, output by result)

1010 NOR-C/R-Value(added to cache, output by result)(with nothing in the cache, behaves like a NOT operation)

1011 XOR-C/R-Value(added to cache, output by result)

1100 A==B-Value(compared to cache, skips the next operation if false)

1101 A>B-Value(compared to cache, skips the next operation if false)

1110 A<B-Value(compared to cache, skips the next operation if false)

1111 <<-Left/Right(output by result)

If the programming is too difficult, I may alter the logic processor to take up less of the instruction set, or add another bit to each program cell to double my oppcodes.

A more speciffic account on how the processor will work: The entire processor hopefully will be clocked at 4hs, however, it will take all four quarters of a second to execute one instruction cycle. The first stage is reading the program memory, the second is translating it into an action and executing it, the third step is reading the resulting value, and the fourth is iterating the counter or executing a GOTO. The processor works on 3kb of cache memory. One is temporary storage for storing the B-variable, typically being loaded up with direct input from a constant or a register. The other is long term storage for the A-variable, which is accessed by the StoreCache instruction. The result is that it works with a smaller program memory cell, but it is relatively inefficient.

One thing I might try to do is change the program counter so that it can work with a pipeline. Difficulty is that it would have to pause on a GOTO every time in case the program can skip it. Any tips on how to reduce the time footprint, or increase the speed is appreciated.

The only things I have not put in are the programming user interface, and the control unit. And possibly a pipeline if the system is too slow.

Another pic:

It is likely that I will perfect this over multiple iterations, as well as develop new models. I will document my progress on this thread.

Any tips and comments would be appreciated.

EDIT: Post reconstruction imminent!

Last edited: