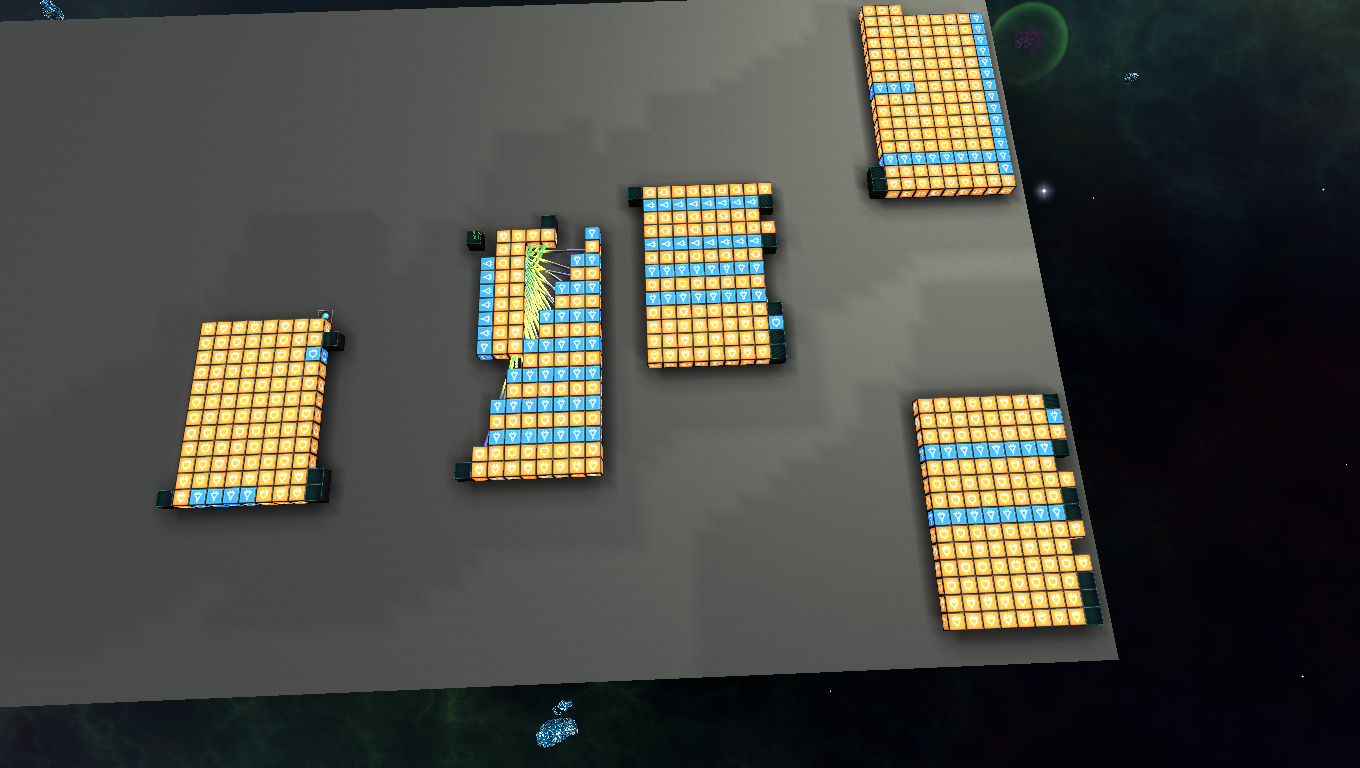

Update: I have remade the ALU components for the new computer:

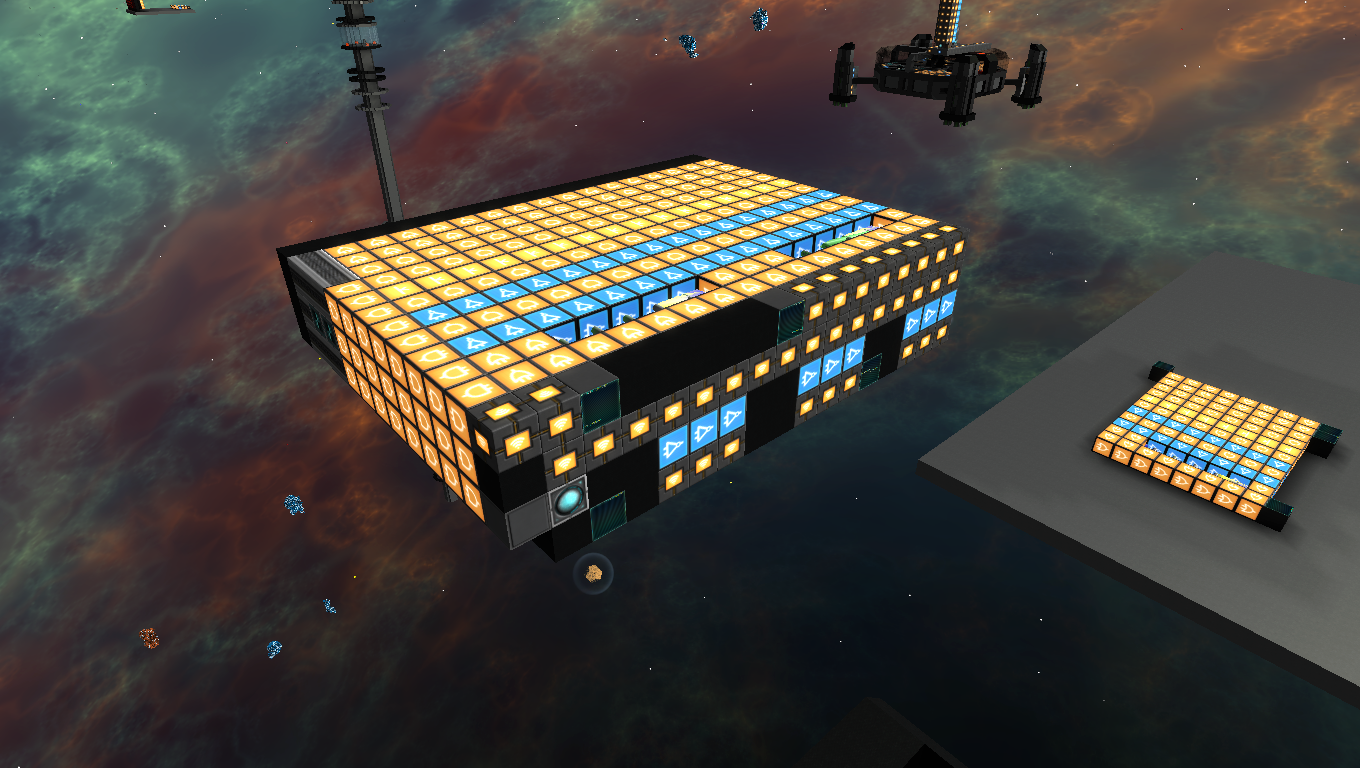

I decided I was going to use a 5-bit oppcode system this time, so I have double the operations to work with. In addition to this, I have no internal oppcodes anymore, instead, I am going to use a multiplexer going directly into the mode pins of the components.

I have also decided to change how individual components are managed. I plan to only send signals through components I want a signal from, unlike the A version. With the A version, it performs many operations at once and chooses the correct output. So if you wanted to perform addition, it also performs a logical comparison and a logical operation. You can imagine this causes extra lag. Lag I hope to avoid by shutting components down when they are not in use.

In the top right is an improved version of the ripple-carry adder I used in the model A version. It is functionally the same as the old one, just smaller.

Below that is a logic processor I have scratch-built for this computer. It supports AND, OR, and XOR. In addition to this, it can invert the results to get NAND, NOR, and XNOR.

To the left of this is my comparison circuit. It takes two inputs and returns whether A and B are equal, A is greater than B, or A is less than B.

To the left of this is an extra comparison circuit. I am not sure what to call it. It is basically a mechanism for fuzzy logic. It takes one input, and then returns the number of bits, as in how many bits are true, versus the number encoded in them. This means you can use this with XOR to get the number of different bits, or XNOR to get the number of same bits. This makes it far easier to write programs than can say "Close enough!" in a scenario like object recognition. But it has no name yet, so I have not made it a template just yet. Any suggestions?

Finally, to the left of this is my binary-shifter. It can shift a number left or right seven places. I plan to use an error checker to check for overflow. If you shift more than seven times, the answer is always going to be 0 no matter what you are shifting.

If there is something I'm missing, or any tips you can give me, please let me know.